이전 글

[Memory management] Memory virtualization, Dynamic relocation, Segmentation

💡Memory virtualization & Address Space - for Abstraction OS는 physical memory를 virtualize하여,각 프로세스가 전체 메모리를 전부 사용하는 것처럼 보이게 한다. Virtual address를 Physical address로 translate하는 것은 OS

intoky.tistory.com

💡3. Paging

메커니즘

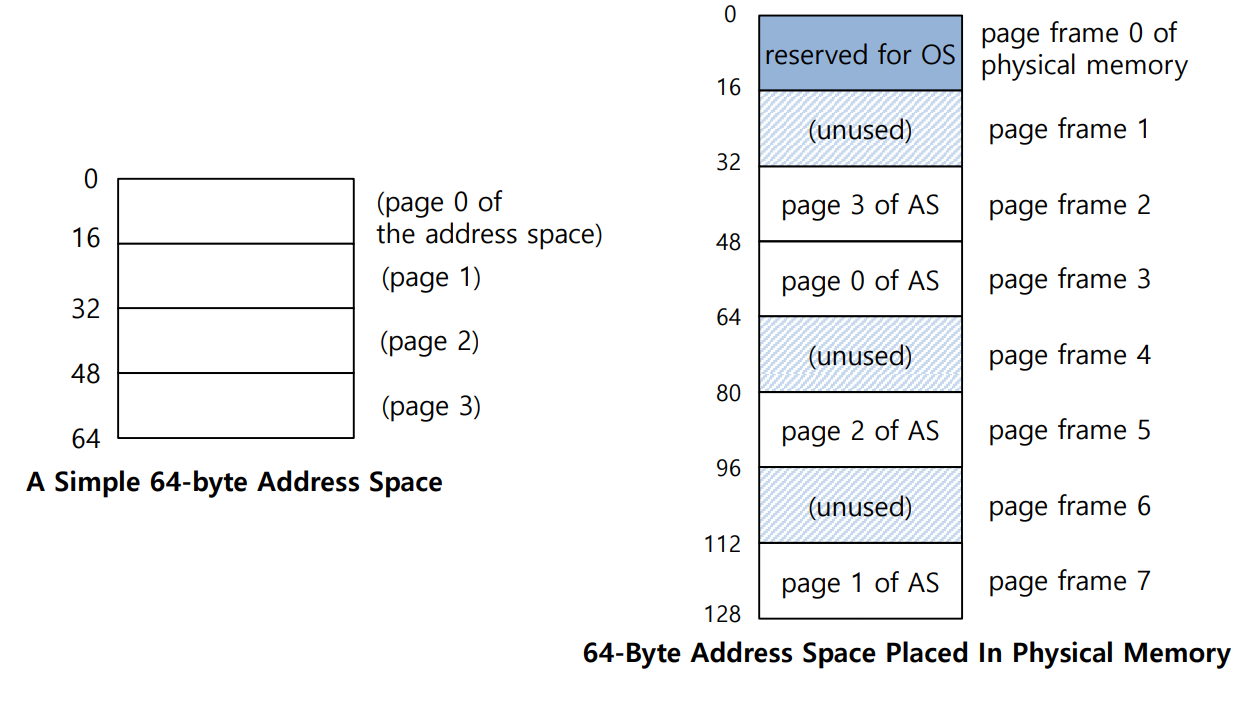

✅page & page frame

address space는 여러 개의 page(고정 크기)로 나뉨,

physical memory는 여러 개의 page frame으로 나뉨

✅Page table: address translation (virtual -> physical)

- entry(=PTE(page table entry))의 array 형태이며, VPN을 이용해 PTE의 주소를 얻을 수 있음.

- 각 process마다 존재함

- 메모리에 존재함

virtual: VPN(Virtual Page Number) + offset

physical: PFN(Page Frame Number) + offset

- offset: virtual과 physical에서 같음. 특정 page 내에서의 주소를 나타냄.

예시

기본적으로,

virtual address: VPN + offset,

physical address: PFN + offset 이다.

이 예시에서는,

address space: 전체 크기 64바이트, page 16바이트

physical memory: 전체 크기 128바이트, page frame 16바이트 라고 하자.

그러면 아래처럼 된다:

- offset: 4비트임.

∵ page의 크기는 16바이트이므로, 즉 16개의 시작 주소를 표현할 수 있어야 하는데, 4비트가 있으면 2^4 = 16개 표현 가능

- VPN: 2비트임.

∵ address space의 전체 크기가 64바이트이고, page는 16바이트이므로, page의 총 개수는 64 / 16 = 4 = 2^2개

- PFN: 3비트임.

∵ physical memory의 전체 크기가 128바이트이고, page frame은 16바이트이므로, page frame의 총 개수는 128 / 16 = 8 = 2^3개

TLB(Translation Lookaside Buffer)

✅TLB가 없을 때: Paging이 너무 느리다.

▶example

아래 코드를 실행한다 생각해보자.

이때 현재 프로세스의 address space는 아래와 같다 하자.

그러면...

a array의 각 요소에 접근할 때마다,

page table look up: 우선 해당 요소가 들어있는 page의 PTE를 찾고 (-> +1회),

memory access: 비로소 해당 요소에 실제로 접근할 수 있다 (-> +1회).

👉총 memory access 횟수 = page table look up 10회 + memory access 10회 = 20회 -> 오래 걸린다.

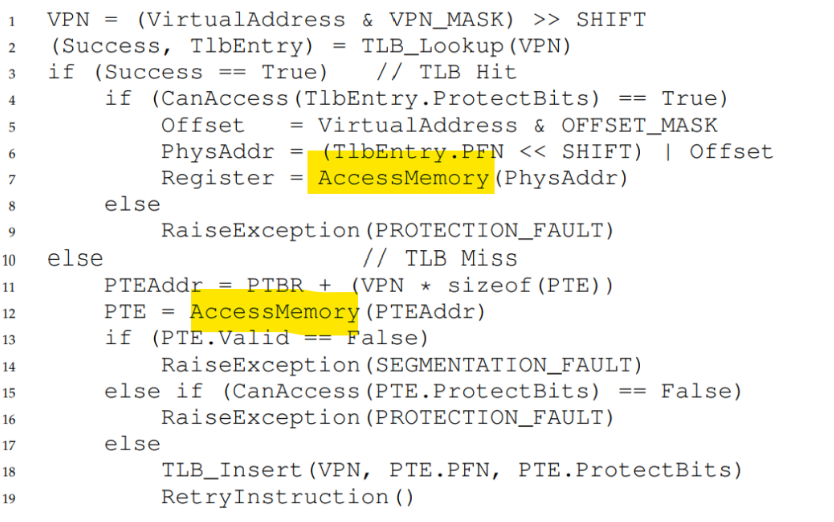

✅TLB가 있을 때: TLB의 메커니즘은?

TLB는 MMU(Memory Management Unit)의 일부이며, 자주 사용되는 virtual->physical address translation의 cache이다.

이를 통해 spatial/temporal locality를 높여 성능을 향상한다.

Fully associative 방식으로 관리된다.

▶example

위 예시를 계속 보자.

여기서는...

a array의 각 요소에 접근할 때마다,

TLB look up: 우선 해당 요소가 들어있는 page의 VPN이

이미 TLB에 있으면 그대로 갖다 쓰고 (-> +0회),

아직 없으면 page table look up을 한다 (-> +1회).

memory access: 비로소 해당 요소에 실제로 접근할 수 있다 (-> +1회).

👉총 memory access 횟수 = page table look up 3회 + memory access 10회 = 13회 -> 좀 빨라졌다.

▶ASID(Address Space Identifier)

두 프로세스가 각자 자신의 address space의 특정 page 정보를 TLB table에 실었는데,

그 page가 VPN이 서로 같다면?! 어느 프로세스의 것인지 어떻게 구별할 것인가?

-> ASID: 해당 page 정보가 온 프로세스의 address space의 ID를 추가적으로 기록해둔다.

강점

- Flexibilty: address space의 효과적인 abstraction

- Simplicity: free-space의 편리한 관리

'컴퓨터과학 > 컴퓨터구조와 운영체제' 카테고리의 다른 글

| [I/O Devices] I/O Bus, Canonical device, Polling & Interrupt, DMA, MMIO (1) | 2024.06.04 |

|---|---|

| [Memory management] Swapping (0) | 2024.05.23 |

| [Memory management] Memory virtualization, Dynamic relocation, Segmentation (0) | 2024.05.01 |

| [운영체제란] 운영체제의 역할, HW의 support (0) | 2024.04.21 |

| [Scheduling in multiple CPU] SQMS, MQMS, CFS, O(1), BFS (0) | 2024.04.20 |